วัตถุประสงค์ของทรานซิสเตอร์ใน CPU ทำหน้าที่เป็นสวิตช์ที่กำหนดชุดคำสั่งหรือไม่ แล้วถ้าเป็นเช่นนั้นแล้วทำไมการเพิ่มจำนวนทรานซิสเตอร์จึงเพิ่มความเร็ว?

การเพิ่มจำนวนทรานซิสเตอร์ในชิปจะเพิ่มความเร็วได้อย่างไร

คำตอบ:

ปิดส่วนหัวของฉัน:

แคชเพิ่มเติมซึ่งเร็วกว่า RAM

คำสั่ง SIMDเพิ่มเติมซึ่งประมวลผลเร็วกว่าคำแนะนำข้อมูลเดียว

แกนเพิ่มเติมเพื่อให้คุณสามารถทำสองสิ่งหรือมากกว่าในครั้งเดียว

ท่อส่งดังนั้นแต่ละคอร์สามารถทำสิ่งต่าง ๆ ได้มากขึ้นในคราวเดียว

ตรรกะการประมวลผลที่ดีกว่าเช่นตรรกะการทำนายสาขาที่ซับซ้อนยิ่งขึ้น

หากคุณอยากรู้เกี่ยวกับสิ่งนี้ฉันขอแนะนำหนังสือThe Elements of Computingโดย Noam Nisan และ Shimon Schocken (อย่างน้อยครึ่งแรก) หลังจากผ่านไปแล้วคุณจะสามารถตอบคำถามของคุณเองอย่างละเอียดด้วยความซาบซึ้งในส่วนที่เกี่ยวข้อง

เว็บไซต์สหายจริงมีบทตัวอย่างบางส่วนและบันทึก มันเป็นหนังสือที่เข้าถึงได้ง่ายมาก ฉันผ่านมันด้วยตัวเองโดยไม่มีปัญหาจากนั้นจึงเข้าชั้นเรียนใหม่ที่มหาวิทยาลัยของฉันซึ่งใช้เป็นข้อความหลัก

คำตอบง่ายๆคือทรานซิสเตอร์ที่มากขึ้นไม่ได้ทำให้ส่วนที่เหลือของพวกเขาเร็วขึ้นแต่แทนที่จะทำอย่างใดอย่างหนึ่งต่อช่วงเวลาเราสามารถทำได้สอง (ด้วยข้อ จำกัด บางอย่าง)

เคนสรุปเหตุผลในคำตอบของเขาไปแล้ว เพื่อขยายตัวต่อไป

- แคชเพิ่มเติมซึ่งเร็วกว่า RAM

เห็นได้ชัดว่าแคชที่ใหญ่กว่าต้องการทรานซิสเตอร์มากกว่า แต่ด้วยทรานซิสเตอร์มากขึ้นเรายังมีทางเลือกของการใช้แคชได้เร็วขึ้น แคชของ CPU เป็นเพียงSRAMซึ่งโดยทั่วไปจะทำจาก 6 ทรานซิสเตอร์ (AKA 6T SRAM) อย่างไรก็ตามเมื่อมีจำนวนทรานซิสเตอร์เพียงพออาจเป็นการใช้เซลล์ SRAM ที่เร็วกว่า แต่ใหญ่กว่าที่ทำจากทรานซิสเตอร์มากกว่า 6 ตัว (เช่น 8T, 10T SRAM)

- คำสั่ง SIMDเพิ่มเติมซึ่งประมวลผลเร็วกว่าคำแนะนำข้อมูลเดียว

ไม่เพียง แต่ SIMD เท่านั้น แต่ยังมีคำสั่งเร่งความเร็วทุกประเภทอีกด้วย ตัวอย่างเช่นสถาปัตยกรรมสมัยใหม่มักจะมีหน่วย AES สำหรับการเข้ารหัส / ถอดรหัสที่รวดเร็วกว่าFMAสำหรับการคำนวณทางคณิตศาสตร์ที่ดีขึ้น (โดยเฉพาะการประมวลผลสัญญาณดิจิตอล) หรือการจำลองเสมือนสำหรับเครื่องเสมือนที่เร็วขึ้น การสนับสนุนคำแนะนำเพิ่มเติมหมายถึงทรัพยากรเพิ่มเติมที่จำเป็นสำหรับการถอดรหัสและดำเนินการ

สิ่งเหล่านี้ค่อนข้างชัดเจน

ในอดีตมีพื้นที่แม่พิมพ์ไม่เพียงพอสำหรับ FPU ดังนั้นผู้คนจึงต้องซื้อแยกต่างหากถ้าพวกเขามีความต้องการสูงของเลขคณิตทศนิยม ด้วยทรานซิสเตอร์ที่มากขึ้นเป็นไปได้ที่จะมี FPU ในตัวเร่งคณิตศาสตร์จุดลอยตัวได้มาก

นอกจากซีพียูที่ทันสมัยsuperscalarและจะพยายามที่จะทำสิ่งที่หลายครั้งโดยการหาอิสระชิ้นข้อมูลและคำนวณพวกเขาก่อนหน้านี้แม้ว่ากระแสการเรียนการสอนเป็นเส้นตรงและแบบอนุกรม ยิ่งพวกเขาสามารถทำสิ่งต่างๆในแบบคู่ขนานได้เร็วเท่าไหร่ ในการทำเช่นนั้น CPU สามารถมี ALU หลายตัวและ ALU สามารถมีหลายหน่วยการดำเนินการ ถ้าเช่น CPU มี 5 ตัวเปรียบเทียบกับ 4 ตัวในรุ่นก่อนหน้านั้นมันทำงานได้เร็วขึ้น 25% ในสถานการณ์ที่มองโลกในแง่ดีที่สุดโดยไม่มีการเปลี่ยนแปลงนาฬิกา ซีพียูที่มีความซับซ้อนมากยิ่งขึ้นใช้การประมวลผลที่ไม่เป็นไปตามลำดับ (ซึ่งเป็นกรณีของซีพียูประสิทธิภาพสูงที่ทันสมัยที่สุด)

- ตรรกะการประมวลผลที่ดีกว่าเช่นตรรกะการทำนายสาขาที่ซับซ้อนยิ่งขึ้น

โดยทั่วไปการดำเนินการสามารถทำได้หลายวิธี หากคุณมีทรานซิสเตอร์มากขึ้นคุณจะมีทรัพยากรมากขึ้นในการใช้เทคนิคที่เร็วขึ้น ตัวอย่างง่ายๆ:

การขยับบิต:

ตัวเปลี่ยนอย่างง่ายทำจากการเชื่อมต่อ flip-flop เข้าด้วยกัน

ที่ต้องการเพียงฟลิปฟล็อปหนึ่งบิตต่อบิตดังนั้นจึงมีขนาดเล็กมาก แต่มันต้องการหนึ่งนาฬิกาเพื่อเลื่อนไปทางซ้ายหรือขวาหนึ่งบิต นั่นเป็นสาเหตุที่ไมโครคอนโทรลเลอร์และซีพียูเล็กฝังตัวมีเพียงคำแนะนำในการเลื่อนทีละตัวเท่านั้น ดู

เมื่อคุณมีทรานซิสเตอร์ที่จะใช้จ่ายมากขึ้นคุณสามารถเปลี่ยนเป็นตัวเปลี่ยนบาร์เรลได้ ตอนนี้ซีพียูสามารถเลื่อนบิตในนาฬิกาเดียวด้วยค่าใช้จ่ายหลายร้อยหรือหลายพันทรานซิสเตอร์

ส่วนที่เพิ่มเข้าไป:

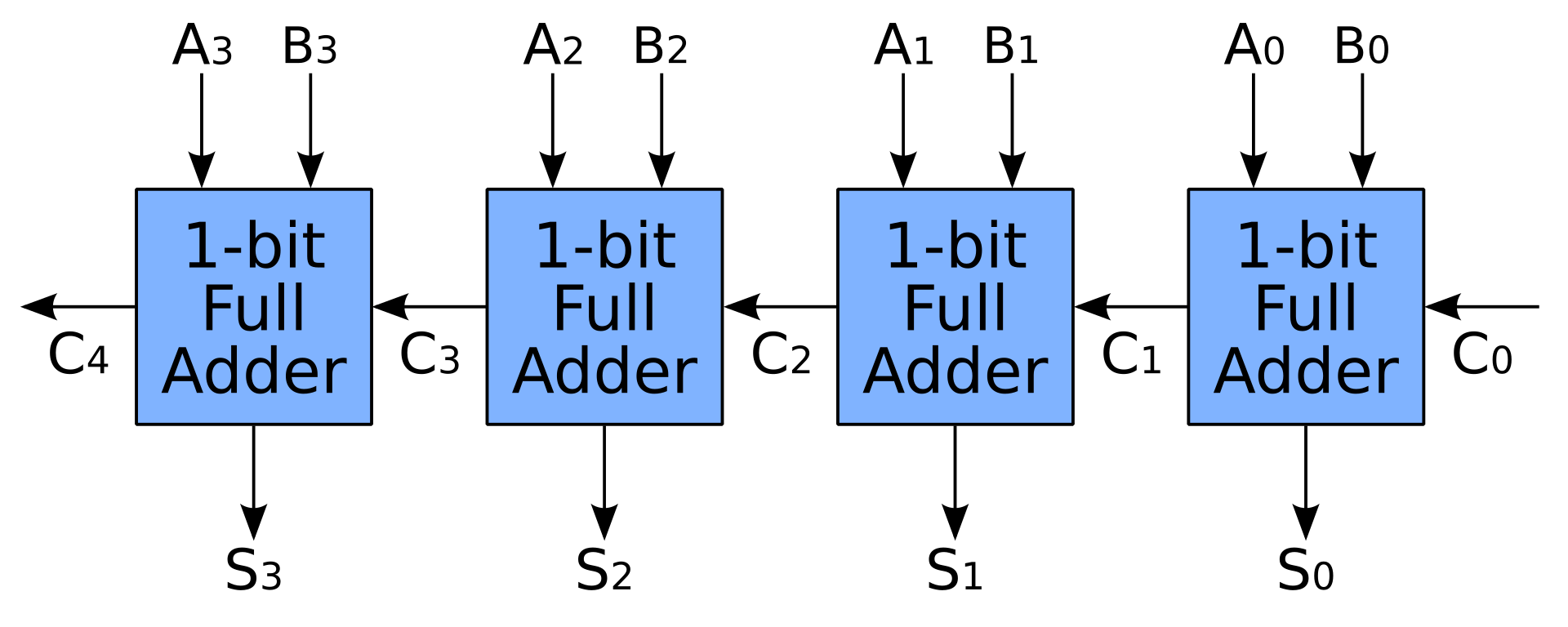

- adder ที่เรียบง่ายจะทำยังโดยการเชื่อมต่อAdders เต็มในซีรีส์ วิธีนี้ตัวบวก N-bit ต้องการนาฬิกา N เพื่อทำงานให้เสร็จซึ่งแน่นอนว่าไม่ใช่สิ่งที่ผู้คนคาดหวังในซีพียู

- ด้วยทรานซิสเตอร์ที่มากขึ้นเราสามารถเพิ่มความเร็วได้โดยการคำนวณการพกพาล่วงหน้าด้วยadder แบบพกพา lookaheadหรือcarry-save adder ส่วนเสริมแบบเต็มยังคงใช้อยู่ แต่จำเป็นต้องใช้พื้นที่มากขึ้นสำหรับหน่วยคำนวณล่วงหน้า

- adder ที่เรียบง่ายจะทำยังโดยการเชื่อมต่อAdders เต็มในซีรีส์ วิธีนี้ตัวบวก N-bit ต้องการนาฬิกา N เพื่อทำงานให้เสร็จซึ่งแน่นอนว่าไม่ใช่สิ่งที่ผู้คนคาดหวังในซีพียู

สิ่งเดียวที่นำไปใช้กับหน่วยงานอื่น ๆ เช่นคูณวงเวียนกำหนดการ ... ยกตัวอย่างเช่นเราสามารถทำคูณอย่างรวดเร็วมากในนาฬิกาเดียวโดยใช้ตรรกะผสม คุณสามารถดูตัวอย่างง่ายๆในคำถามตัวคูณแบบ 3 บิต - พวกมันทำงานอย่างไร . แต่ทรานซิสเตอร์ที่ต้องการจะเพิ่มขึ้นเป็นกำลังสองของความกว้างอินพุตดังนั้นซีพียูขนาดเล็กที่มีตัวคูณใช้ตรรกะแบบต่อเนื่องแทนเพื่อประหยัดพื้นที่จำนวนมากสำหรับตัวคูณ:

สถาปัตยกรรมแบบทวีคูณที่เก่ากว่านั้นใช้ shifter และตัวสะสมเพื่อรวมผลิตภัณฑ์บางส่วนแต่ละชิ้นซึ่งมักจะเป็นผลิตภัณฑ์บางส่วนต่อรอบการซื้อขายความเร็วรอบสำหรับพื้นที่ตาย สถาปัตยกรรมตัวคูณที่ทันสมัยใช้อัลกอริทึม (แก้ไข) Baugh – Wooley ต้นไม้ Wallace หรือตัวคูณ Dadda เพื่อเพิ่มผลิตภัณฑ์บางส่วนเข้าด้วยกันในรอบเดียว ประสิทธิภาพของการนำวอลเลซมาใช้ในบางครั้งก็มีการปรับปรุงโดยการดัดแปลง Booth ที่เข้ารหัสหนึ่งในสองแบบหลายค่าซึ่งช่วยลดจำนวนของผลิตภัณฑ์บางส่วนที่จะต้องรวม

https://en.wikipedia.org/wiki/Binary_multiplier#Implementations

เมื่อคุณมีทรานซิสเตอร์จำนวนมากคุณสามารถใช้ตรรกะเชิงผสมเพื่อทำ FMA ซึ่งใช้ทรัพยากรมากกว่าตัวคูณ

คอมพิวเตอร์สมัยใหม่อาจมี MAC เฉพาะซึ่งประกอบด้วยตัวคูณที่ใช้ในตรรกะเชิงผสมตามด้วย adder และตัวสะสมตัวสะสมที่เก็บผลลัพธ์ เอาต์พุตของรีจิสเตอร์จะถูกป้อนกลับไปยังอินพุตหนึ่งของ adder ดังนั้นในแต่ละรอบนาฬิกาเอาต์พุตของตัวคูณจะถูกเพิ่มในรีจิสเตอร์ ตัวคูณแบบผสมต้องใช้ตรรกะจำนวนมาก แต่สามารถคำนวณผลิตภัณฑ์ได้เร็วกว่าวิธีการขยับและเพิ่มคอมพิวเตอร์ทั่วไปก่อนหน้านี้

การเพิ่มจำนวนทรานซิสเตอร์มักจะทำโดยทำให้มีขนาดเล็กลงซึ่งจะทำให้พวกเขาเข้าใกล้กันมากขึ้นซึ่งจะช่วยลดเวลาในการแพร่สัญญาณ